Analog Devices Finds Winning A/D Circuit Designs in EECS 511

Congratulations to Jeong, Park, and Yoon!

Enlarge

Enlarge

In a course that is designed to give students critical experience designing analog to digital converters, Integrated Analog/Digital Interface Circuits (EECS 511), students also competed for prizes thanks to the support of Analog Devices. EECS 511 is taught by Prof. Michael Flynn, an expert in analog and mixed-signal circuits, and in particular circuits that transfer information between the analog and digital domains.

Enlarge

Enlarge

The design that earned first place, and a prize of $1500, was, “A 6-bit 10 GS/s Time-Interleaved 2 bit/step SAR ADC,” by Jaehun Jeong, Seokjun Park, and Dongmin Yoon, all graduate students in the electrical engineering program.

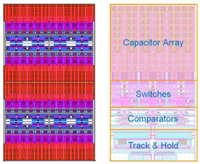

In this work, shown to the right, a 6-bit 10 GS/s ADC is implemented in IBM 0.13 μm CMOS process. 16 unit 625MS/s SAR ADCs convert signals in 10 GS/s. To achieve an effective sampling rate of 10 GS/s, a four-phase clock generator provides clocks to each ADC block of 4 unit SAR ADCs. Each ADC block consists of a controller, a track and hold circuit, capacitor DACs, and comparators. Two unit SAR ADCs share the same track and hold circuit, resulting in a total of eight track and hold circuits. The circuit was designed to handle an input range of 1.2 Vp-p with common mode. ENOB of 5.5 bit was achieved with ideal clock source and 4.5 bit was measured with a multi-phase clock generator at input signal of 4.92 GHz.

Second place and $500 was awarded Bharan Giridhar, Amir Javidi, and Gyouho Kim for their project, “An Energy-Efficient 9-bit Charge Pump Based Pipelined ADC.”

MENU

MENU