Student teams earn prizes for their ADC circuit designs in EECS 511

Enlarge

Enlarge

Students in the graduate level course, Integrated Analog/Digital Interface Circuits (EECS 511), competed for cash prizes while presenting their final design projects thanks to the support of Analog Devices, Inc. The winning projects were designed for battery-operated mobile applications as well as instrumentation and measure applications.

EECS 511 is taught by Prof. Michael Flynn, an expert in analog and mixed-signal circuits, analog-to-digital conversion, and other interface circuits.The top four projects were sent to Analog Devices, where a group of senior circuit designers selected the following two winning teams:

First Place ($1,500)

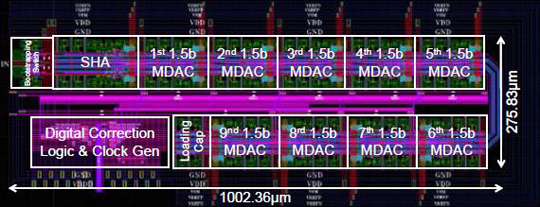

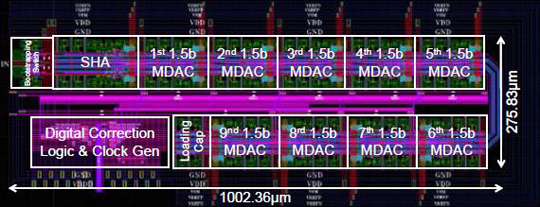

A 50MS/s, 10.5-Bits, 21.3fJ/conv.steps Pipeline ADC using Ring Amplifier, by Yong Lim, Mehmet Batuhan Dayanik, and David Moore

Enlarge

Enlarge

“The power efficiency of the analog-to-digital converter (ADC) is one of the most important features for battery-operated mobile applications,” stated Yong. “This work is based on the concept of the ring amplifier introduced at ISSCC 2012. We improve the power efficiency of the pipeline ADC by a factor of about two compared to the state of the art for pipeline ADCs by improving the ring amplifier’s power efficiency. We were able to reduce power consumption without sacrificing performance. A 1.5b per stage with total of 10.5-bits 50MS/s pipeline ADC is implemented in 0.13 µm CMOS as a proof of concept prototype. The simulated effective number of bits is 10.17bits for a Nyquist frequency input. The power consumption is only 1.22mW.”

Second Place ($500)

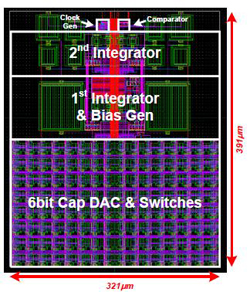

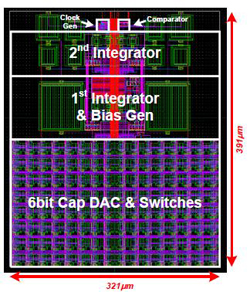

18b Incremental Zoom-ADC in 0.13µm CMOS, by Seok-hyeon Jeong, Wanyeong Jung, and

Sechang Oh

Enlarge

Enlarge

Enlarge

Enlarge

In this project, the students described their project as an energy-efficient, high-resolution incremental analog-to-digital converter (ADC) for instrumentation and measurement applications. Instead of using a conventional sigma-delta architecture, a two-step conversion which combines 6bit course SAR and 13bit fine sigma-delta achieves high resolution as well as energy efficiency. The complete ADC is implemented in 0.13µm CMOS. Simulation results give an effective number of bits (ENOB) of 18 bits and ±1.6ppm integral nonlinearity (INL).

MENU

MENU